## Nanoscale

## SUPPLEMENTARY INFORMATION

## First demonstration of 2T0C-FeDRAM: a-ITZO FET and double gate a-ITZO/a-IGZO FeFET with record-long multibit retention time of > 4-bit and > 2000 s

Tae Hyeon Noh,<sup>†a</sup> Simin Chen,<sup>†a</sup> Hyo-Bae Kim,<sup>b</sup> Taewon Jin,<sup>a</sup> Seoung min Park,<sup>a</sup> Seong Ui An,<sup>a</sup> Xinkai Sun,<sup>a</sup> Jaekyun Kim,<sup>a</sup> Jae-Hoon Han,<sup>d</sup> Ji-Hoon Ahn,<sup>\*b</sup> Dae-Hwan Ahn,<sup>\*d</sup> and Younghyun Kim<sup>\*a</sup>

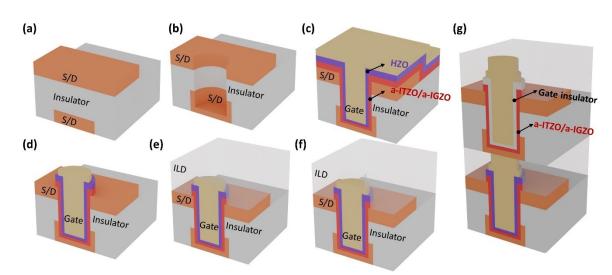

Fig. S1. Process flow of one channel all around (CAA) structure 3D 2T0C-FeDRAM cell (The 3D 2T0C-DRAM process was proposed by Duan *et al.*<sup>2</sup> Here, the main differentiation is the introduction of the ferroelectrics of HZO after channel formation as a gate insulator.) (a) MIM structure deposited by S/D spacer and top electrode in sequence after bottom electrode formation, (b) channel region etching, (c) gate stack deposition by ALD in sequence ( $R_{tr}$  gate stack: a-ITZO/a-IGZO/HZO/gate electrode,  $W_{tr}$  gate stack: a-ITZO/gate insulator/gate electrode ), (d) active region isolation (e) Inter-Layer dielectric (ILD) deposition, (f) ILD etching, (g) After the lower  $R_{tr}$  is completed, the upper  $W_{tr}$  repeats the same process.

<sup>a.</sup> Department of Photonics and Nanoelectronics, BK21 FOUR ERICA-ACE Center, Hanyang University, Ansan 15588, Korea.

Electronic Supplementary Information (ESI) available: [details of any supplementary information available should be included here]. See DOI: 10.1039/x0xx00000x

<sup>&</sup>lt;sup>b.</sup> Department of Materials Science and Chemical Engineering, Hanyang University, Ansan, Republic of Korea

<sup>&</sup>lt;sup>c</sup> Korea Institute of Science and Technology, Seoul, Republic of Korea

<sup>&</sup>lt;sup>+</sup> Both authors equally contributed to this work.

<sup>\*</sup> Corresponding authours

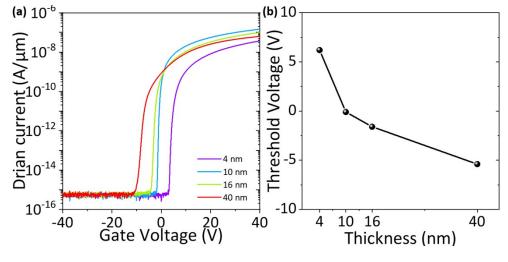

Fig. S2. (a) Transfer characteristics of a-ITZO (4, 10, 16, and 40 nm-thickness) FETs. (b) Thickness dependence of threshold voltage for a-ITZO TFTs.

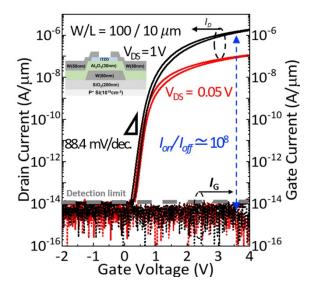

Fig.S3.  $I_D - V_G$  characteristics of the write a-ITZO FET. Utilizing high mobility near 25.5 cm<sup>2</sup>/V s and low leakage current attributes of a-ITZO, a low S.S. value of 88.4 mV/dec. and an off current below 10<sup>24</sup> A/ $\mu$ m were achieved, making it suitable as a write transistor ( $W_{tr}$ ) for 2TOC-FeDRAM.

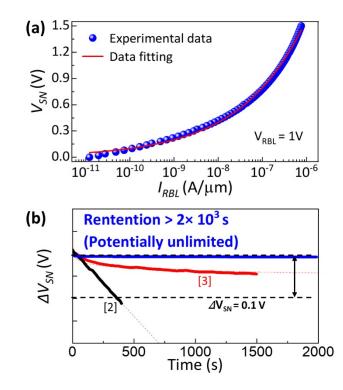

Fig. S4. (a) Data fitting of  $V_{SN}$ - $I_{RBL}$ , detected during the 2TOC-FeDRAM read operation,  $V_{SN}$  can be extracted. (b)  $V_{SN}$  changes vs. time, indicating that the excellent retention time.  $I_{RBL}$  was maintained almost without the voltage dropping for a period of 2000 s.<sup>2, 3</sup>

## Notes and references

- 1. X. Duan, K. Huang, J. Feng, J. Niu, H. Qin, S. Yin, G. Jiao, D. Leonelli, X. Zhao and Z. Wang, *IEEE Trans. Electron Devices*, 2022, **69**, 2196-2202, DOI: <u>http://dx.doi.org/10.1109/TED.2022.3154693</u>.

- 2. A. Belmonte, H. Oh, N. Rassoul, G. Donadio, J. Mitard, H. Dekkers, R. Delhougne, S. Subhechha, A. Chasin and M. Van Setten, presented in part at the 2020 IEEE International Electron Devices Meeting (IEDM), 2020.

- 3. K. Chen, Z. Zhu, W. Lu, M. Liu, F. Liao, Z. Wu, J. Niu, B.-M. Kang, W. Dan and X.-S. Wu, presented in part at the 2023 International Electron Devices Meeting (IEDM), 2023.

This journal is © The Royal Society of Chemistry 20xx

**Journal Name**