## **Electronic Supplementary Information**

## Logic Inverters Based on the Property Modulated Si Nanowires by Controlled Surface Modifications

Kyeong-Ju Moon, a Tae-Il Lee, Woong Lee, and Jae-Min Myoung\*

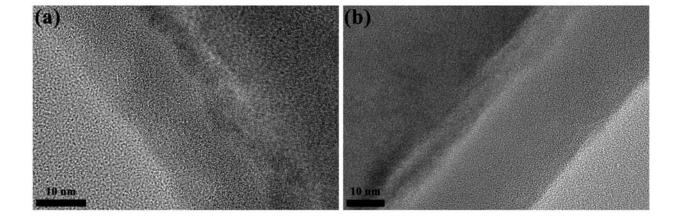

**Figure S1.** TEM images of heat treated *n*-type Si NWs for (a) 10 and (b) 20 min at 900 °C. The surface of Si NWs was oxidized to SiO<sub>2</sub> at the rate of 1.3 nm a minute. The surface of NW is smoother than as synthesized NW.

<sup>&</sup>lt;sup>a</sup> Department of Materials Science and Engineering, Yonsei University, 134 Shinchondong, Seoul, 120-749, Korea. Fax:

<sup>+82-2-365-2680;</sup> Tel: +82-2-2123-2843; E-mail: jmmyoung@yonsei.ac.kr

<sup>b</sup> School of Nano & Advanced Materials Engineering, Changwon National University, 9 Sarim-Dong, Changwon, Gyoungnam 641-773, Korea.

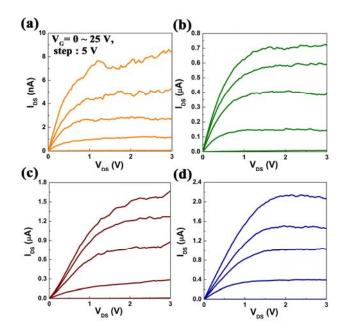

**Figure S2.** Output characteristics ( $I_{DS}$ – $V_{DS}$ ) of (a) as-synthesized *n*-type Si NWs and heat treated Si NWs for (b) 10, (c) 20, and (d) 30 min.

**Table S3.** The electrical properties in each state were represented by numerical table

|                                                                | as-synthesized | 10 min         | 20 min        | 30 min          |

|----------------------------------------------------------------|----------------|----------------|---------------|-----------------|

|                                                                |                |                |               |                 |

| Mobility<br>(cm²/Vs)                                           | 1 ~ 40         | 40 ~ 100       | 110 ~ 440     | 190 ~ 450       |

| Subthreshold swing (V/decade)                                  | 1.4 ~ 4.0      | 1.4 ~ 2.1      | 1.4 ~ 2.3     | 1.3 ~ 2.1       |

| $\begin{array}{c} Threshold \ voltage \\ (V_{th}) \end{array}$ | <b>−2 ~ 9</b>  | <i>−</i> 3 ~ 5 | <b>−6 ~ 1</b> | <b>−12 ~ −5</b> |

| Yield (%)                                                      | 9              | 67             | 92            | 89              |

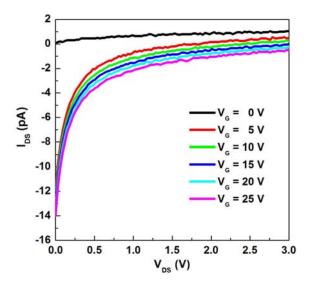

**Figure S4.** Typical  $I_{DS}$ — $V_{DS}$  relations measured on a test structure prepared by depositing Ag and Au electrodes on cured PVP/SiO<sub>2</sub> without Si NWs.